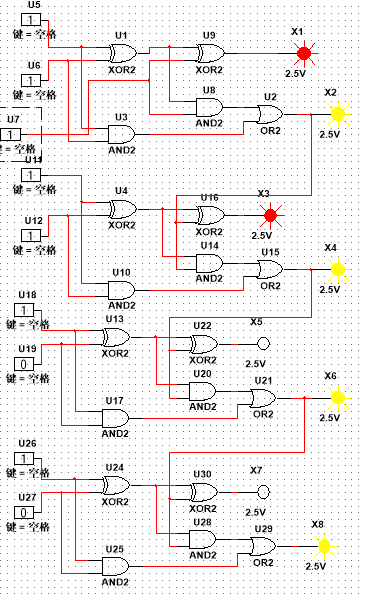

16位全加器逻辑电路图

|

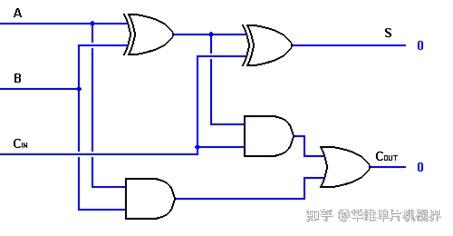

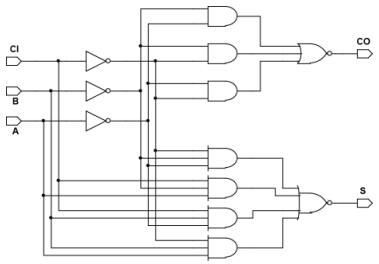

全加器逻辑电路图

实用一位加法电路

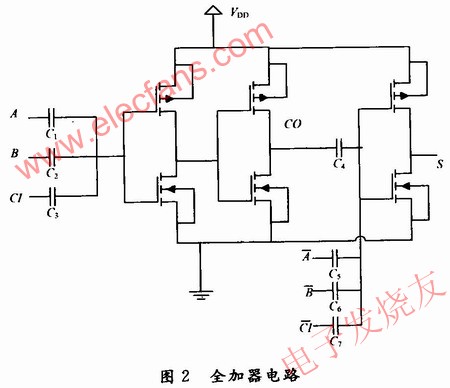

全加器电路

全加器逻辑电路图

全加器

全加器电路

华理数字逻辑实验二全加器

电子/电路 一位全加器实验电路方法的研究 4 种门电路来实现,逻辑电路

全加器,要求有实验原理,函数表达式,卡诺图,逻辑电路图和proteus模拟

数字电路与逻辑设计:用74138实现一位全加器!

课题名称组合逻辑全加器

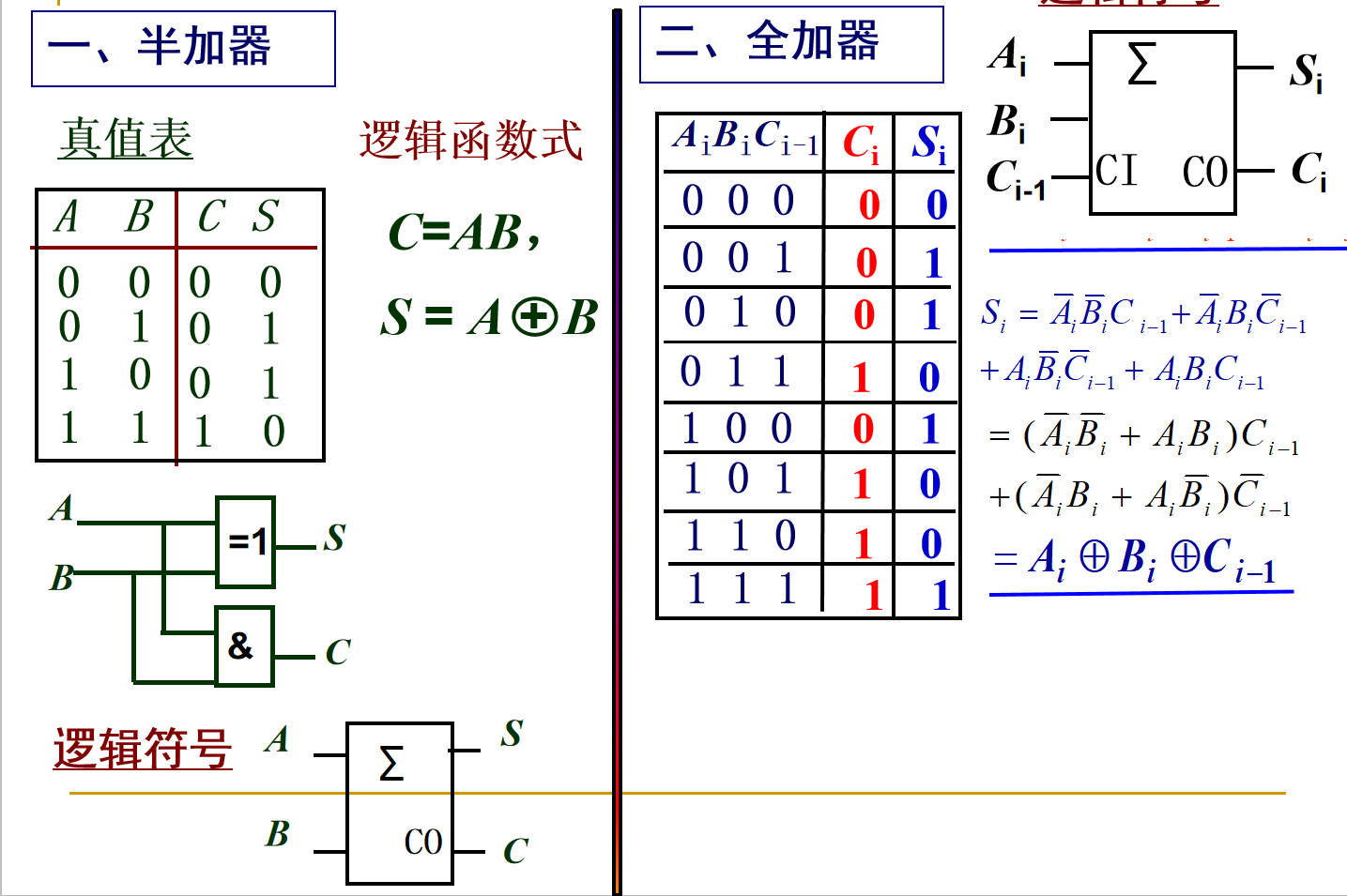

加法器可以实现对两个n位的二进制数的加运算,一般由半加器和全加器

全加器电路,包括:数据输入电路模块,数据输入电路模块包括逻辑与门和

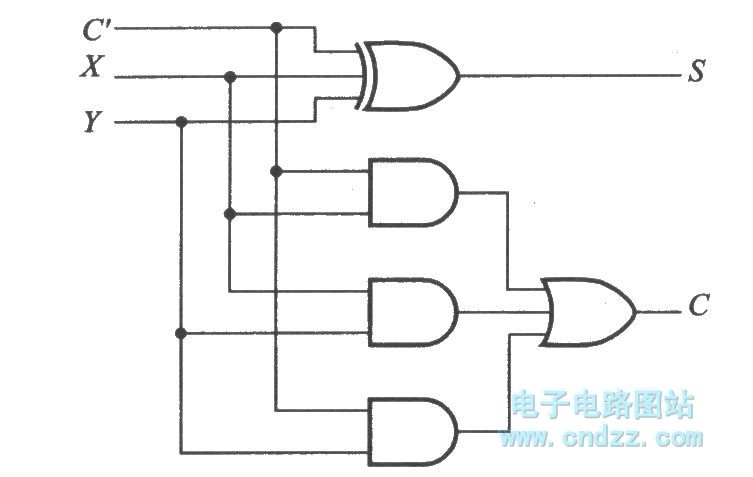

减法运算电路图 使用半加器和全加器的4位加法运算电路图

一位全加器原理图:1111111001101011001001101010100011000000xiyici

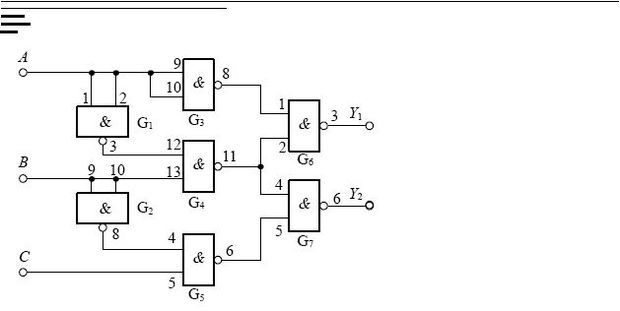

如何只用与非门实现全加器,求逻辑图

用4:1数据选择器实现全加器逻辑功能

从零开始搭建一个8位计算机系列二搭建4位全加器

74ls0074ls0874ls32全加器的ad原理图和pcb源文件

单片机入门数字电路基础之什么是半加器,什么是全加器

数字电路与逻辑设计:用74138实现一位全加器!

全加器 全加器能进行加数,被加数和低位来的进位信号相加,并根据

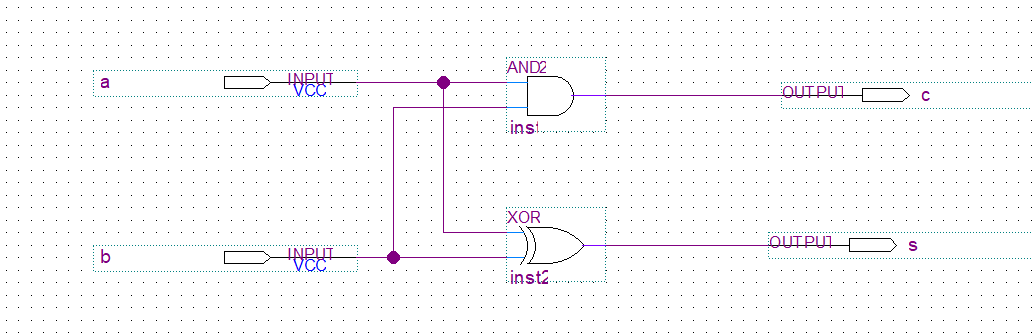

简单数字电路1

实验12: 组合逻辑电路

基于多数决定逻辑门的全加器电路设计

一位全加器电路版图设计

用两片4位二进制加法器实现8位二进制加法电路图如p1所示,根据对应a8

fpga设计入门

验证4位全加器的逻辑功能

加法器原理16位先行进位 |

-

请勿采集本站,如有疑问请联系管理员!