四位并行加法器逻辑图

|

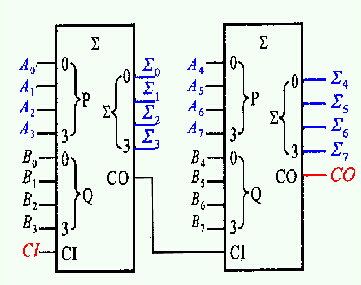

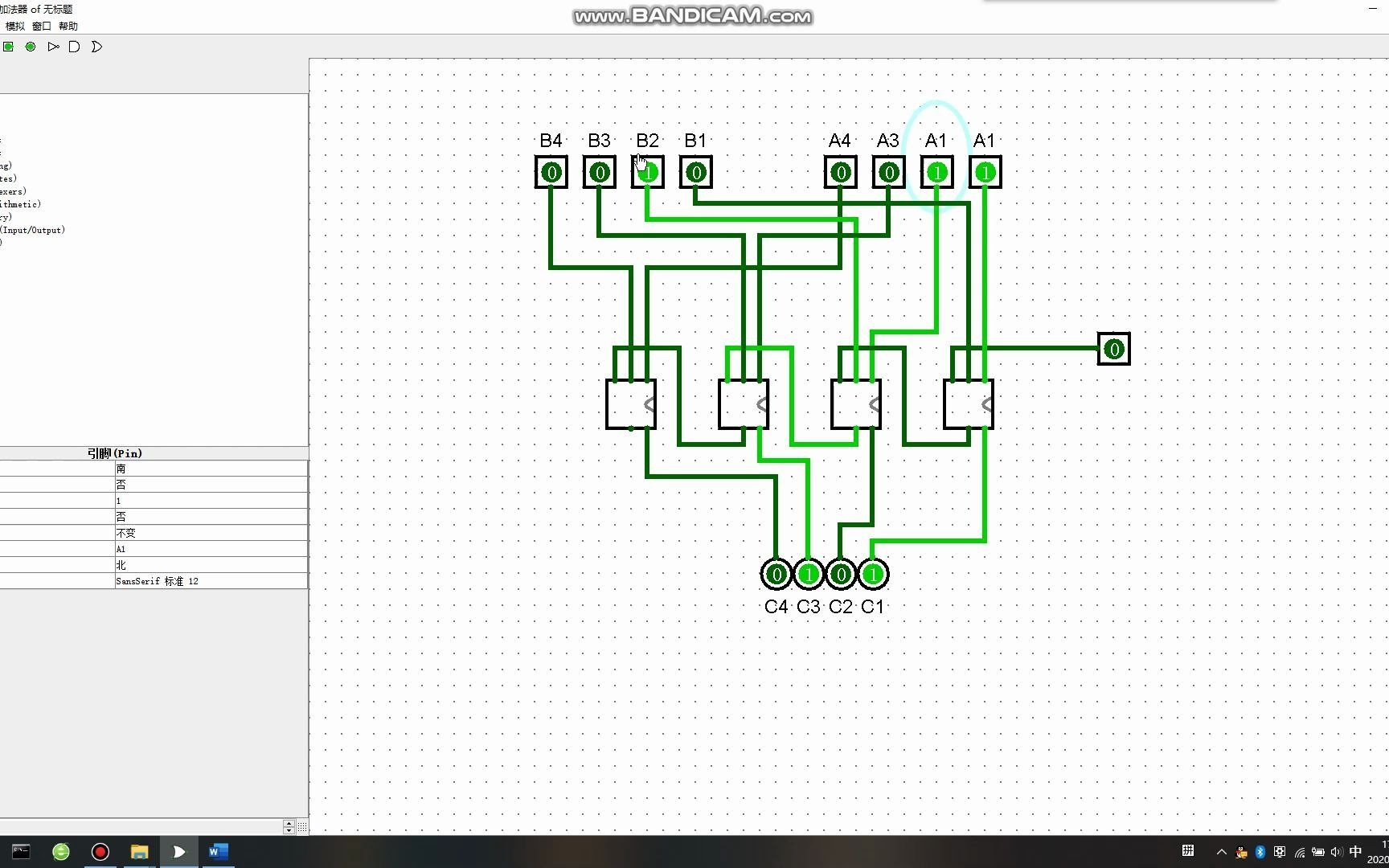

例2逻辑图导出过程图4是用2个4位加法器模块构成8位加法器的逻辑

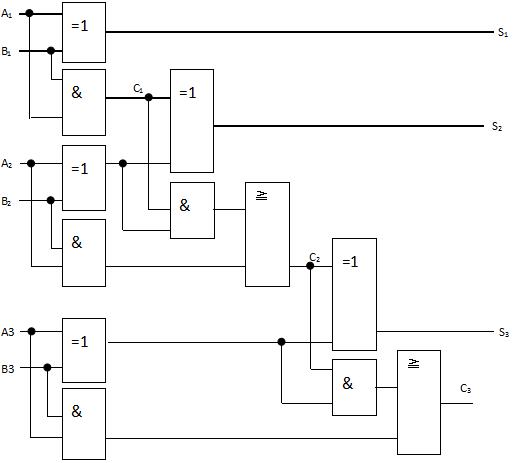

四位并行加法器设计

4位并行加法器

【计算机组成实验】四位加法器

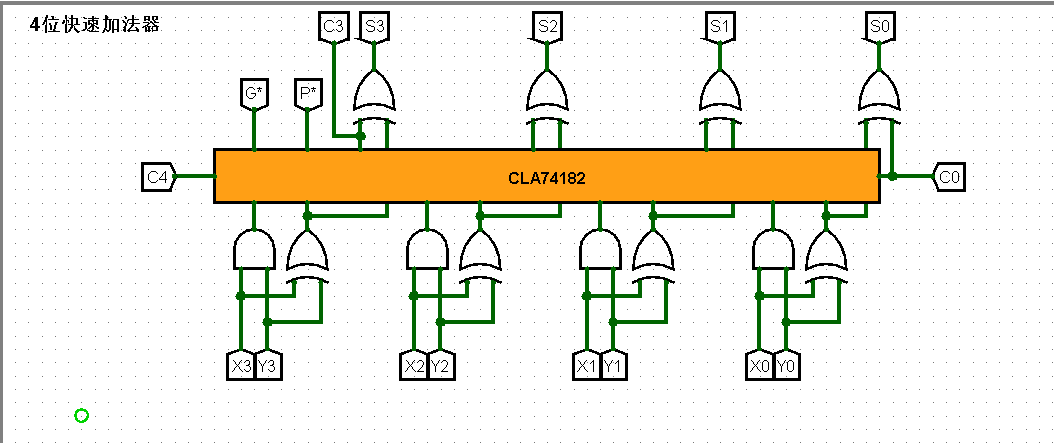

[logisim] 四位并行加法器 (四位先行进位加法器)

4位并行加法器

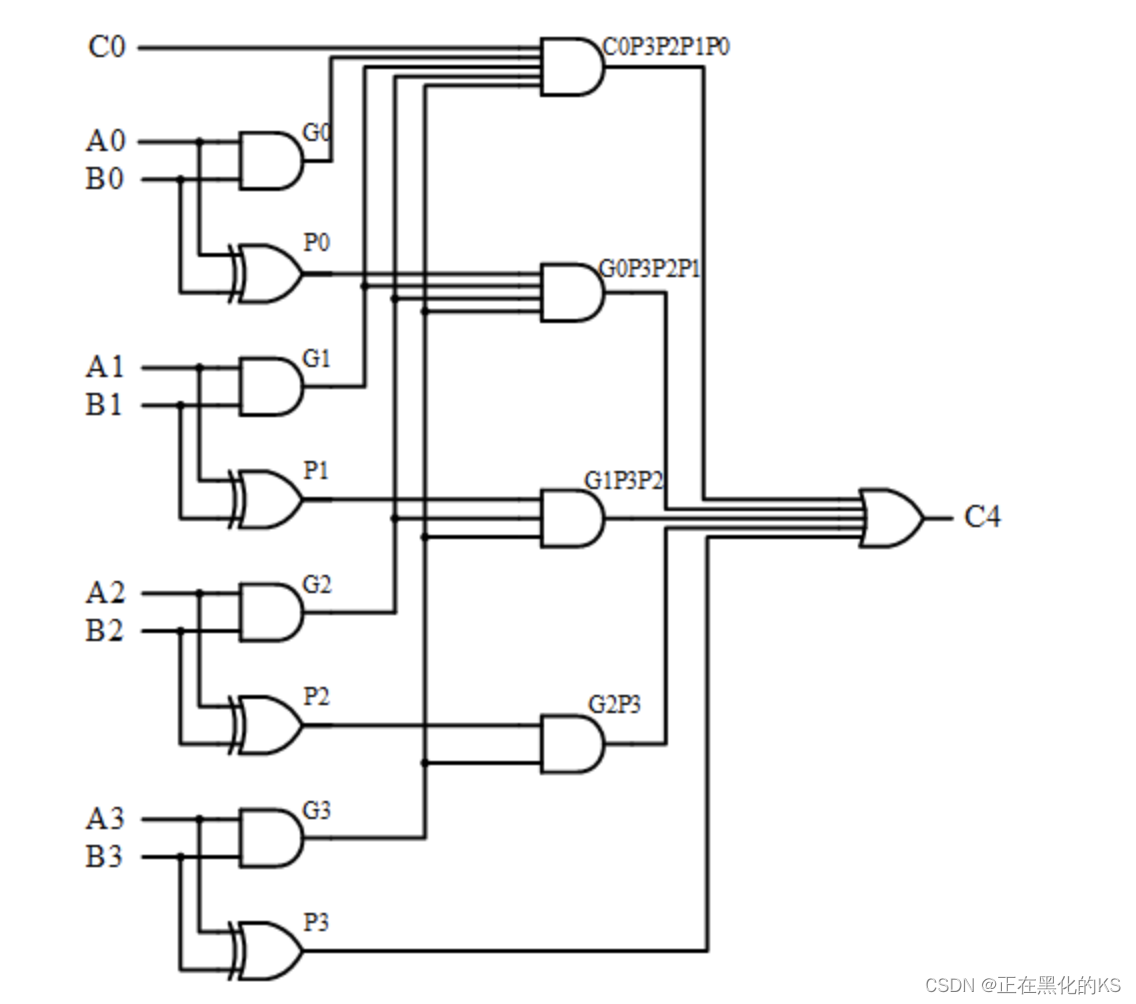

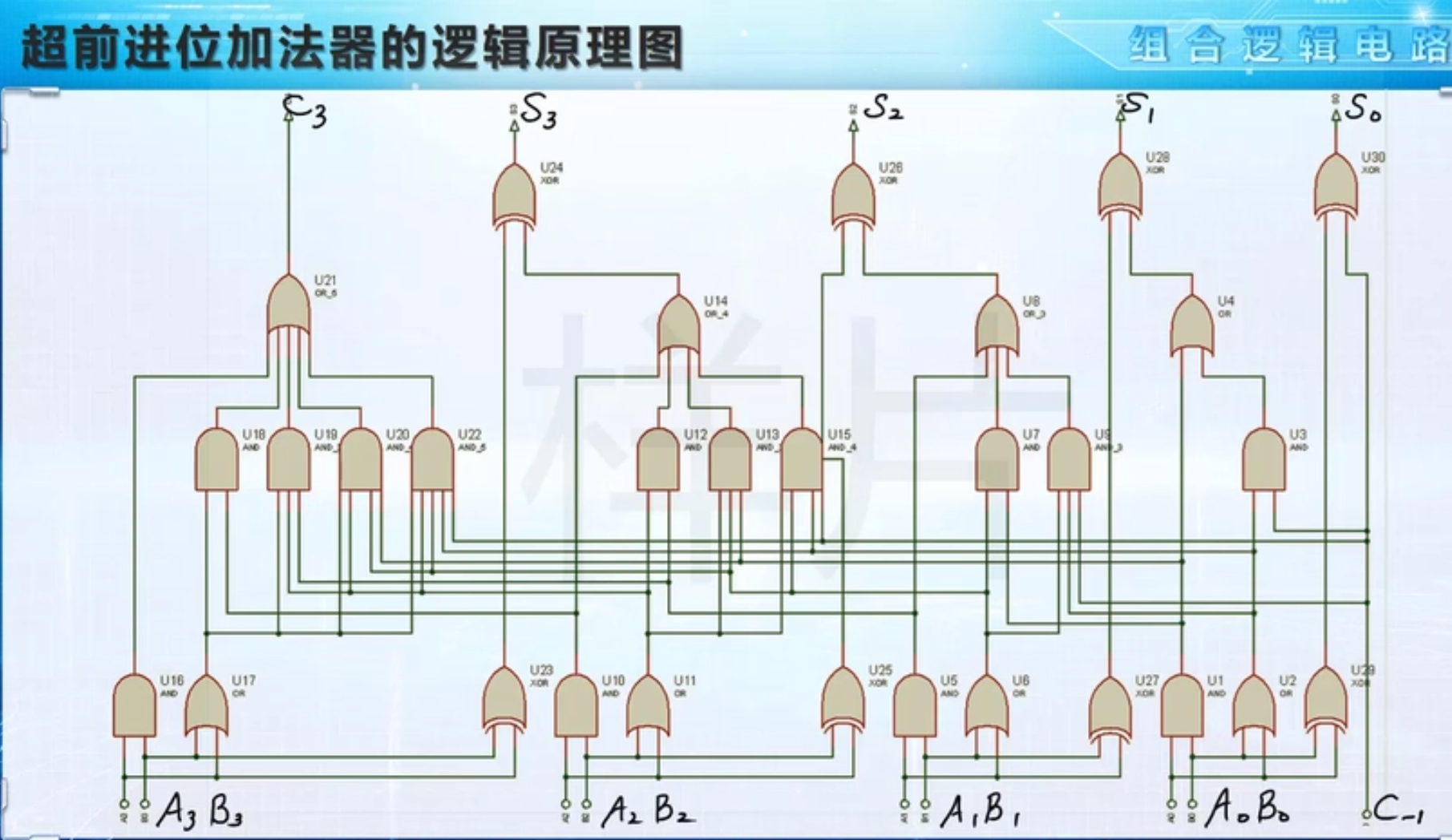

4位先行进位加法器

使用全加器的4位加法运算电路图

4位并行加法器

由四位并行进位全加器74ls283构成图所示

4位超前进位加法器设计

使用全加器的4位加法运算电路图

使用全加器的4位加法运算电路图

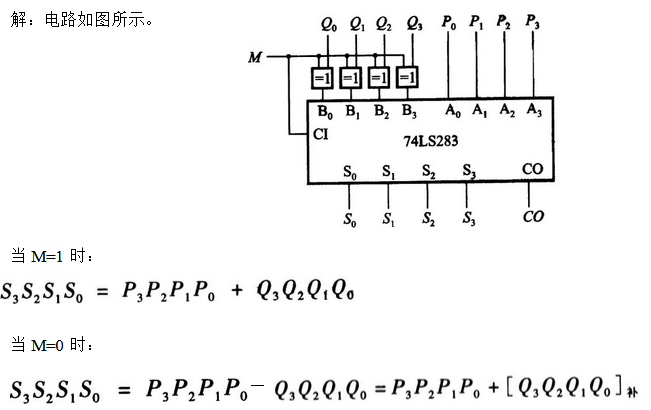

试用并行4位加法器连接成将余三码转换成8421bcd代码的转换电路

超级全加器的4位加法运算电路图

logisim 4位快速加法器

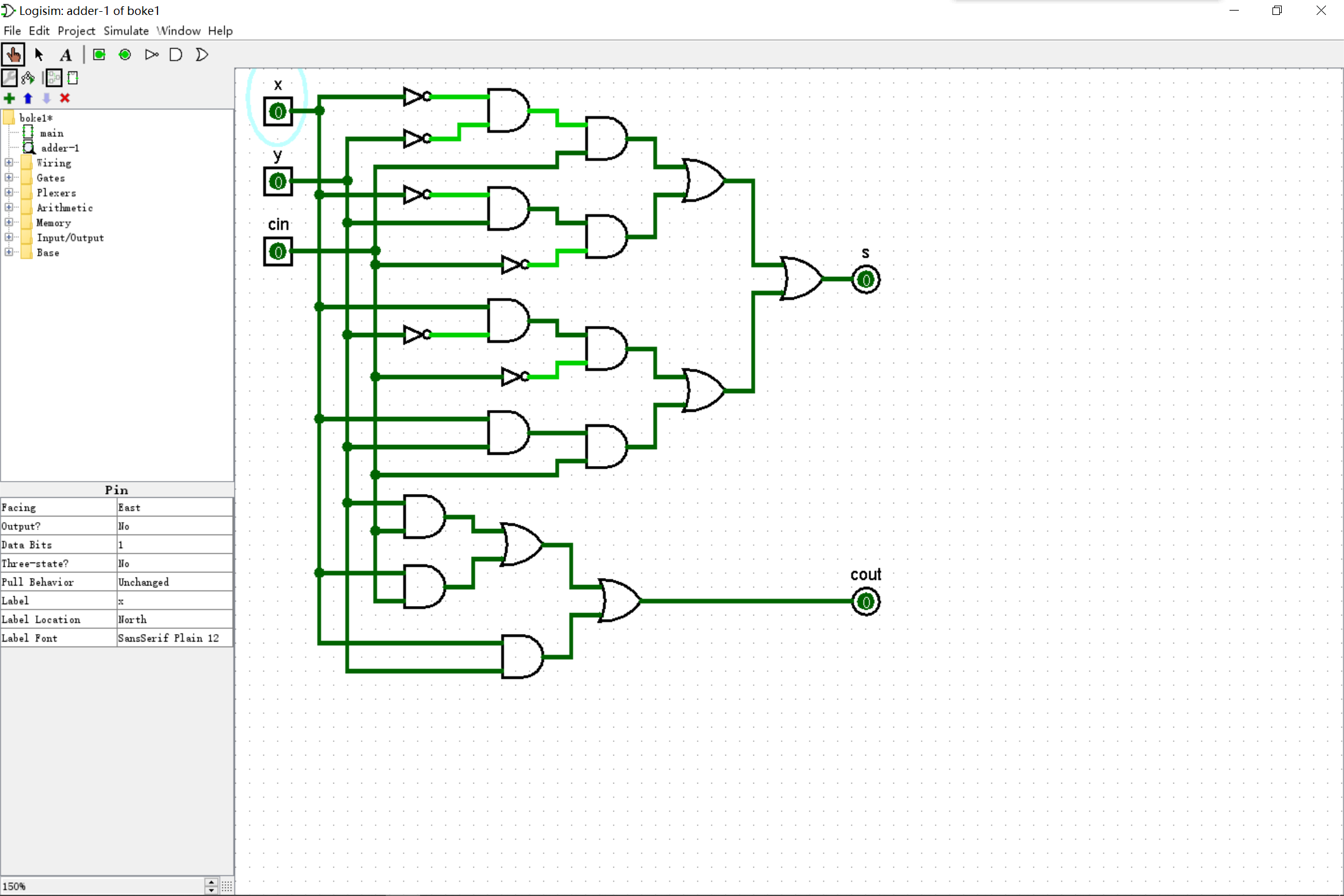

多位加法器(2)全加器:考虑来自低位的进位③逻辑图②真值表s =a ⊕ b

试用4位并行加法器74ls283设计一个加/减运算电路

verilog串行四位加法器和超前四位加法器74hc283

logisim4位加法器的实现

四位二进制加法器

logisim之4位全加器实现以及七段数码管显示

图 fpga实现的四位涟波进位加法器

四位加法器的电路图

四位全加器74ls83完成四位二进制加法怎么做

logisim 4位快速加法器

「verilog学习笔记」4bit超前进位加法器电路

4位超前进位加法器设计

加法器的设计

sn74f283nsrg4 |

-

请勿采集本站,如有疑问请联系管理员!

![[logisim] 四位并行加法器 (四位先行进位加法器) [logisim] 四位并行加法器 (四位先行进位加法器)](https://img-blog.csdnimg.cn/6c4779e0d91c4239a138952cae57cea6.png#pic_center)