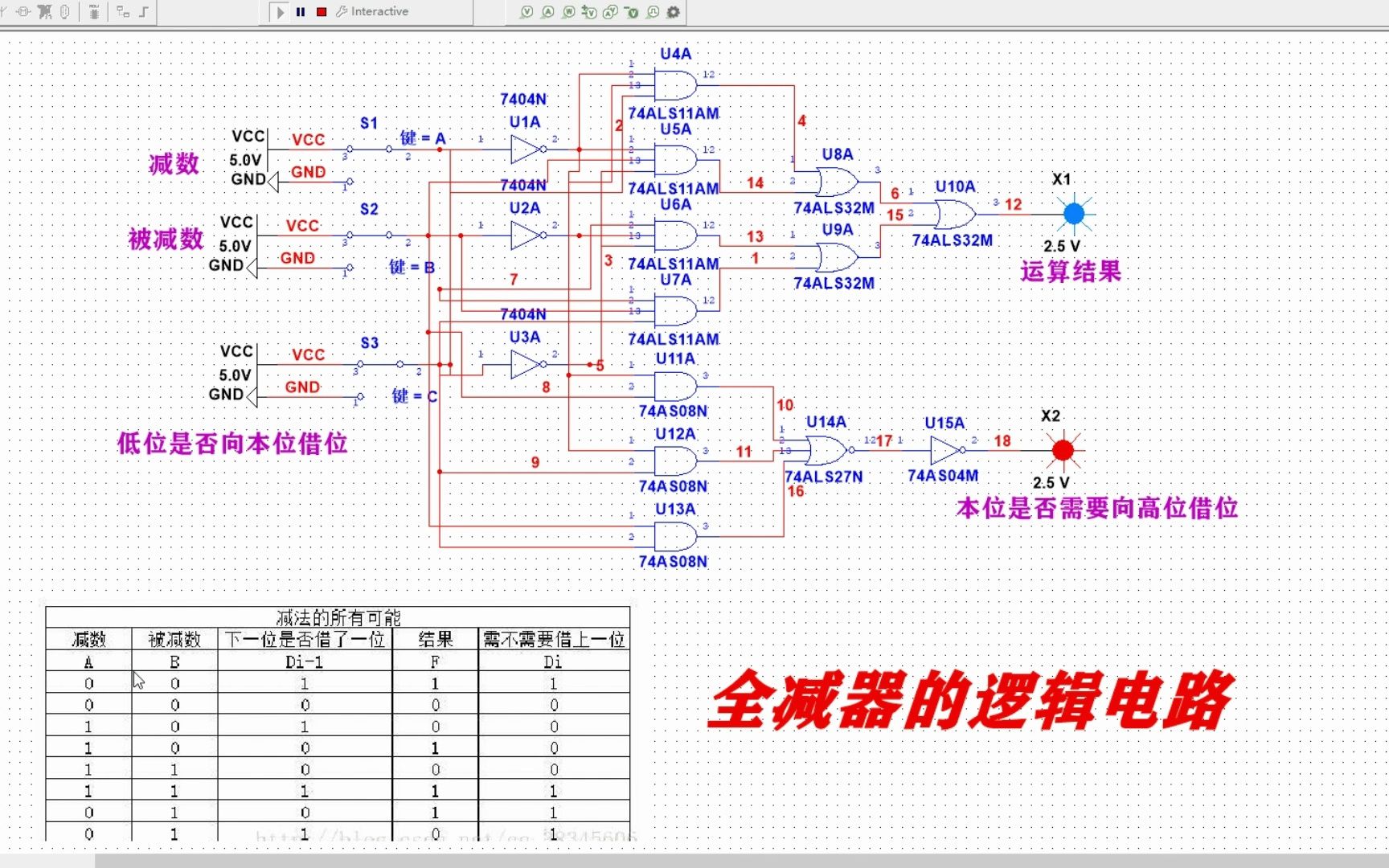

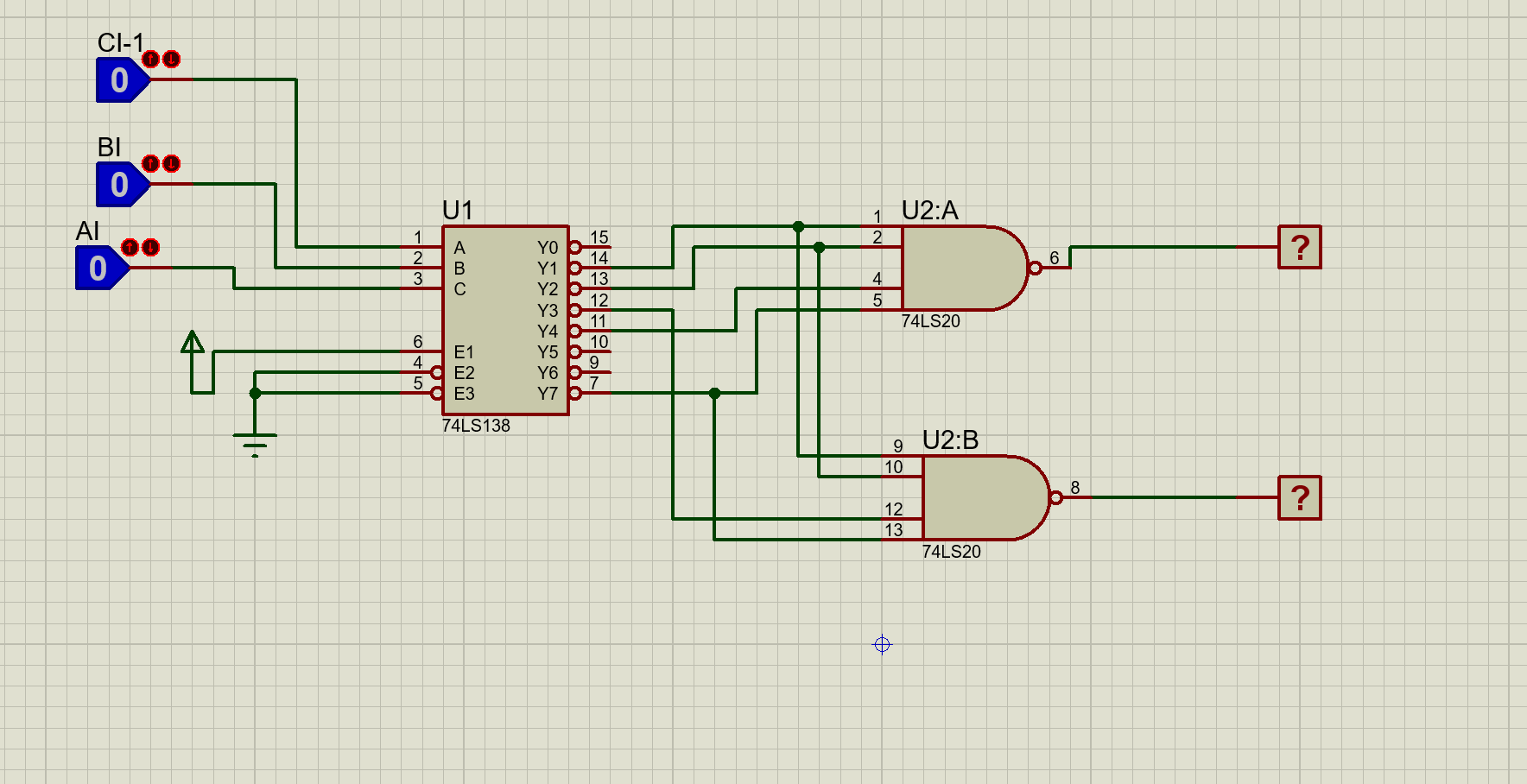

153全减器逻辑电路图

|

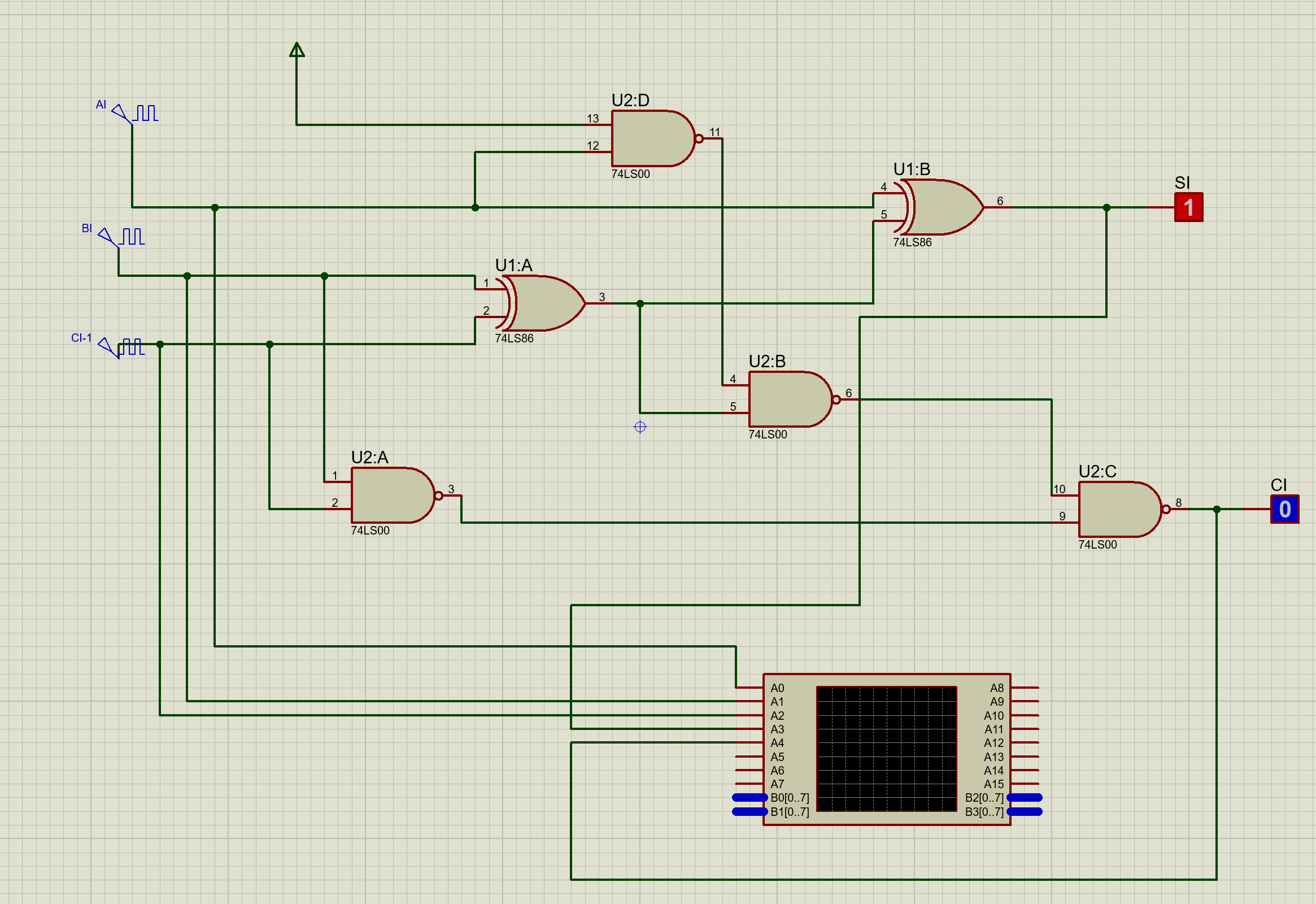

全减器的逻辑电路multisim仿真数电设计

一位全减器逻辑电路图

全减器逻辑电路图

仿照全加器画出1位二进制数的全减器:输入被减数为a,减数为b,低位来的

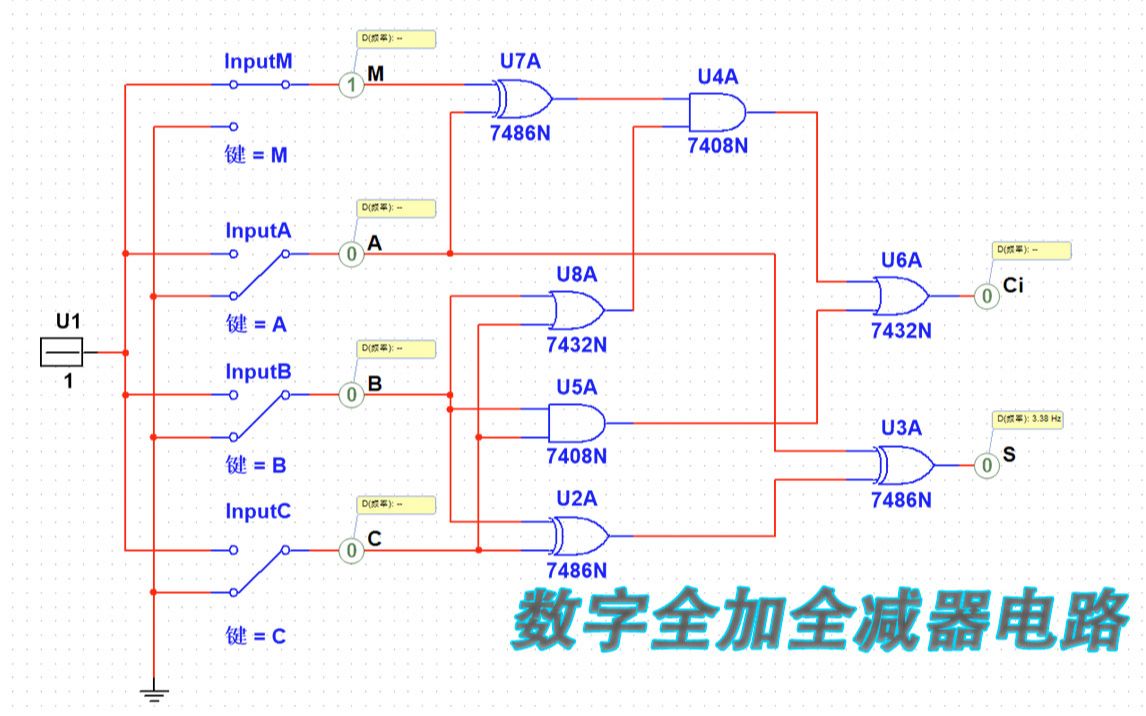

设计一个全减器电路

cumt矿大

全减器

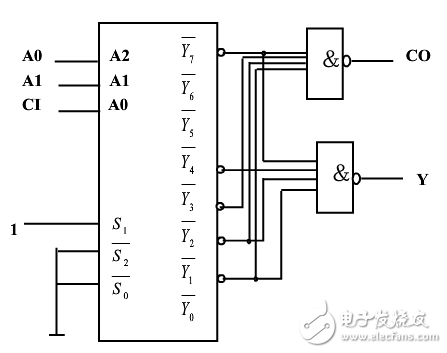

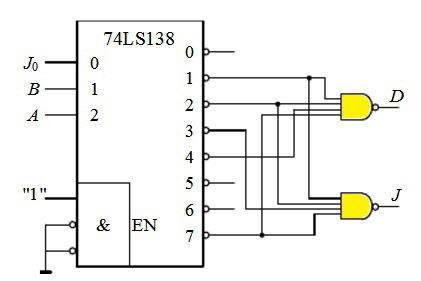

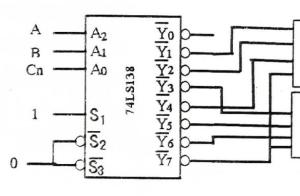

74ls138三线—八线译码器实现,逻辑图如下: 全减器

数字电路 全减器设计(最后结果与非式)

设计一个一位全加减器,采用异或门和与非门来实现该电路 设一控制变量

这是38译码器设计的1位二进制全减器,输入为被减数,减数,和来自低位的

74ls138设计一位二进制全减器

数字电路 全减器设计(最后结果与非式)

当a=0,b=1时,能实现y=1的逻辑运算是()

如图逻辑电路为()电路[图]a 延时动作,瞬时返回b 瞬

cumt矿大

用74ls138和门电路设计1位二进制全减器出错 真值表不符

或数据选择器74ls151设计一个监测信号灯工作状态的逻辑电路

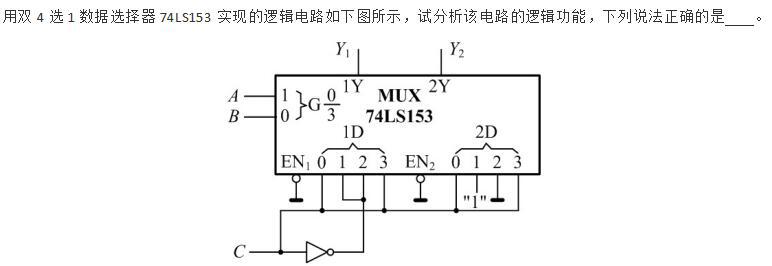

74ls153逻辑图

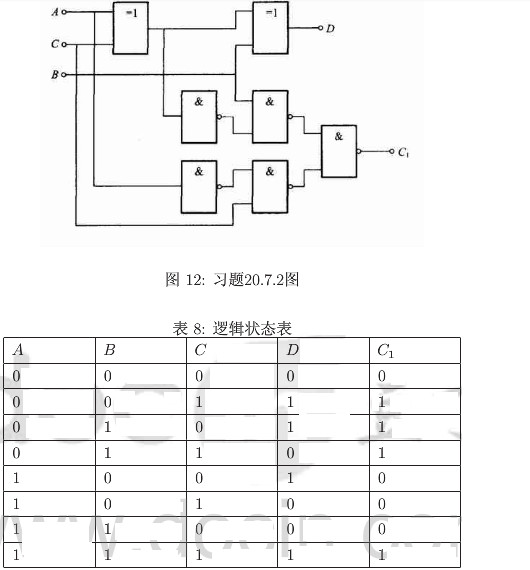

分析逻辑电路,需要列出真值表,表达式,结论,感谢

用74ls138实现一位全减器

410全加器全减器

三款减法器的电路图解析

减法器电路原理图

用vhdl结构描述设计一全减器

用74ls138和与非门实现全减器逻辑电路

4位的加法运算减法运算电路

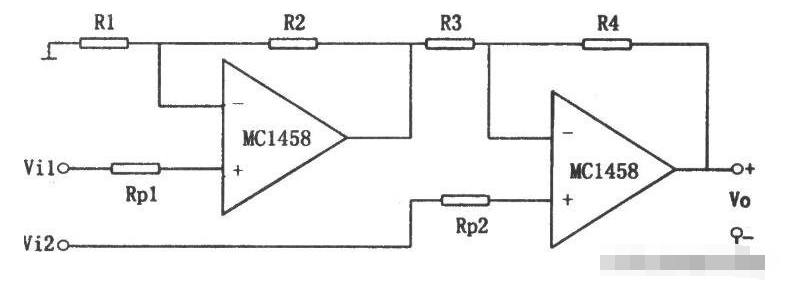

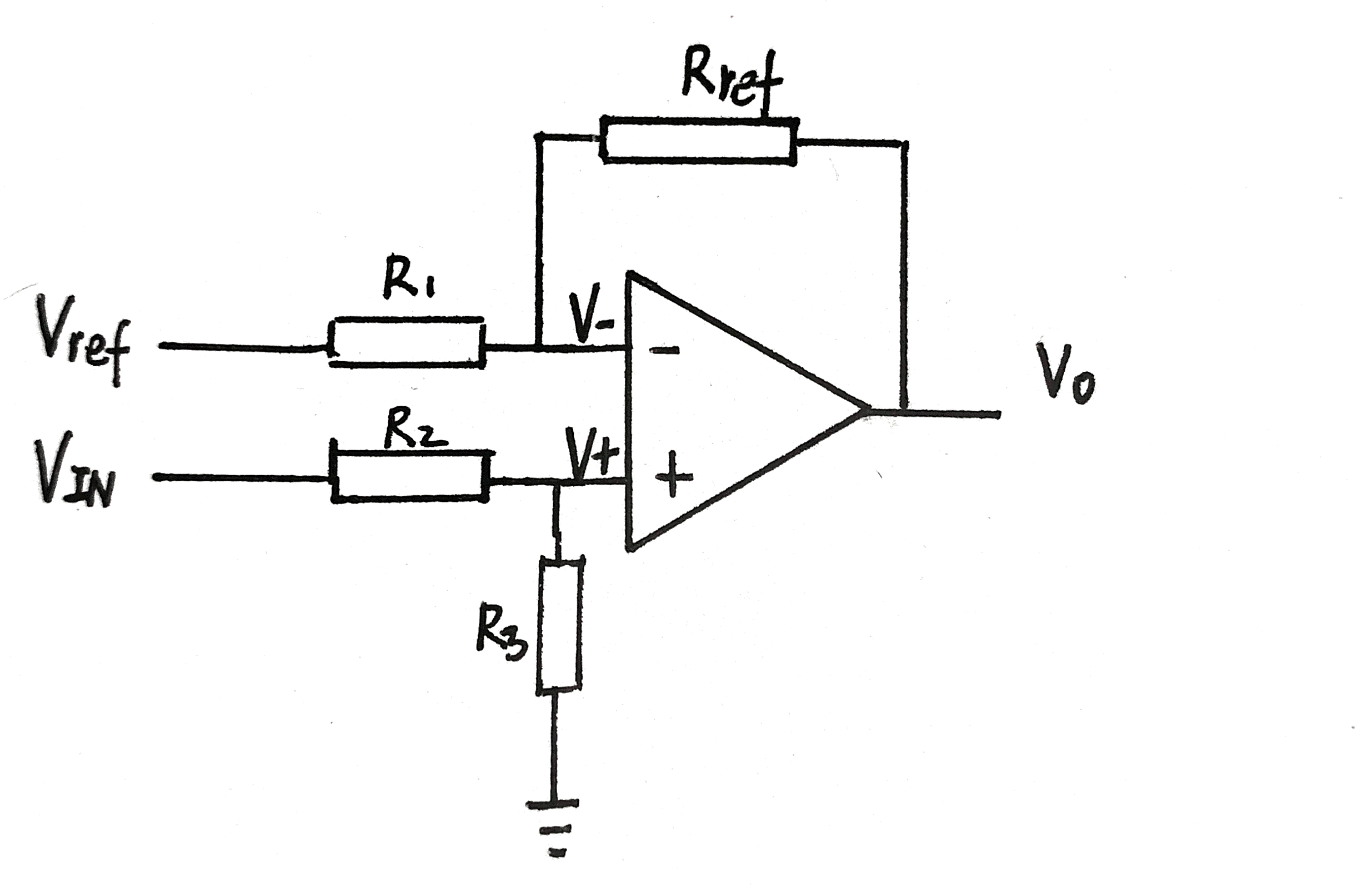

所示是减法运算电路,讹通过ri加到运算放大器的反相输入端,蚰通过r2

【减法电路】实现0v~ 5v输入

杨颂华 冯毛官 孙万蓉 第4章 组合逻辑电路 图411 例41 |

-

请勿采集本站,如有疑问请联系管理员!

![如图逻辑电路为()电路[图]a 延时动作,瞬时返回b 瞬 如图逻辑电路为()电路[图]a 延时动作,瞬时返回b 瞬](https://static.jiandati.com/519d2be-chaoxing2016-269979.png)