74ls112触发器引脚图

|

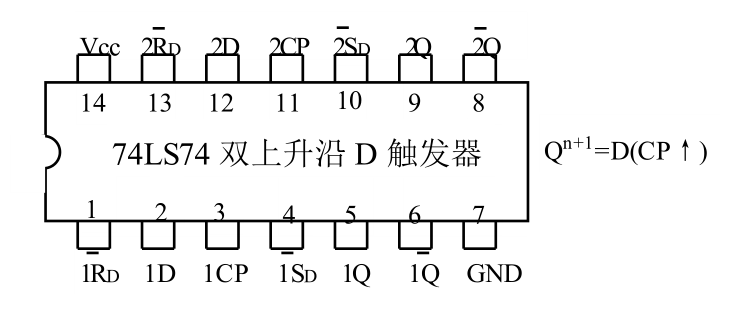

74ls74为集成d触发器芯片,每个芯片中包含两个d触发器

关于74ls74触发器说法正确的是

74ls123 可重触发双稳态触发器 74ls124

触发器的功能测试及应用 建筑电气

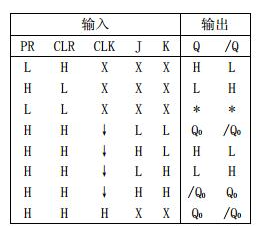

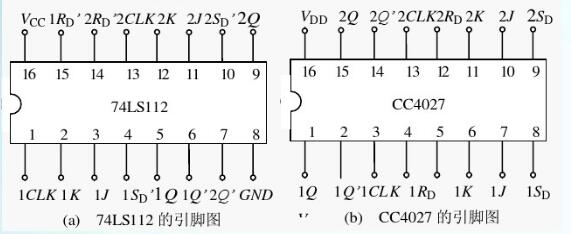

图3 74ls112双jk触发器引脚排列及逻辑符号表3 74ls112的功能表输入

数电实验 触发器功能测试ppt

电子元器件采购网平台

数字电路实验设计:d触发器组成的4位异步二进制加法计数器

带清除和预置端的高速cmos双jk负沿触发器cc74hc112(74hc112)(1) 功能

74ls192的引脚图 74ls192的功能表如表1所示

时序电路(计数器,移位寄存器)

如图3

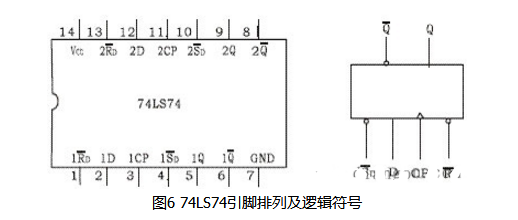

图6 74ls74引脚排列及逻辑符号表5 74ls112的功能表

74ls112a,74f112,74als112,74s112,74hc112双j

74ls175四d 触发器(a41)

74ls112引脚图 引脚图 vcc 1rd 2rd 2cp 2k 2j

时长02:37[ ]实验步骤

74ls11芯片管脚图:74ls32芯片管脚图:74ls112芯片管脚图

74ls174等六d型触发器(带清除端)

74ls112引脚图及功能表

74ls74 双上升沿 d 触发器

充值 pc客户端 考试大全 违法和不良信息举报 在线客服 四d触发器74ls

1,74ls112为clk 下降沿触发2,cc4027为clk 上升沿触发且其异步输入端

图6

直插 74ls112 带预置清除负触发双j

集成触发器及其应用 本次实验选用74ls112双jk触发器,74ls74双d触发器

所有分类 自然科学 化学 触发器及其应用ppt jk触发器( 74ls112,74ls

2017全国电赛综合测评四分频电路(一片d触发器74ls74的两种方法,有图

74ls74引脚图和逻辑图 四,实验内容 1用d触发器构成4分频器 第1页

下列关于双jk集成触发器74ls112引脚功能叙述中,错误的是ls112引脚图 |

![时长02:37[ ]实验步骤 时长02:37[ ]实验步骤](https://file1.elecfans.com/web2/M00/81/E5/wKgZomQb9RqAZPvMAABPhzJadAw419.jpg)