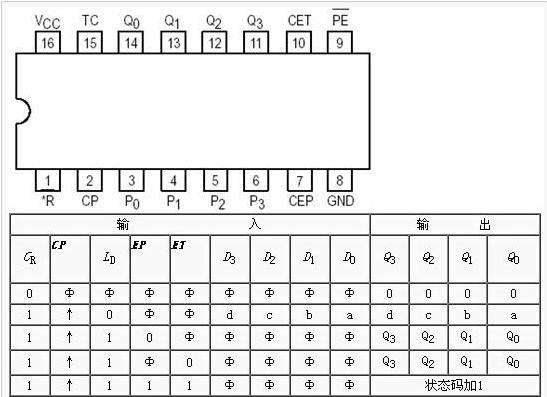

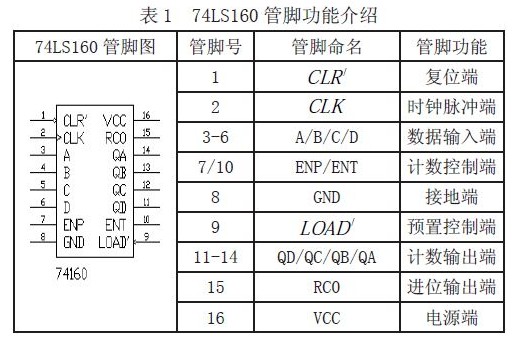

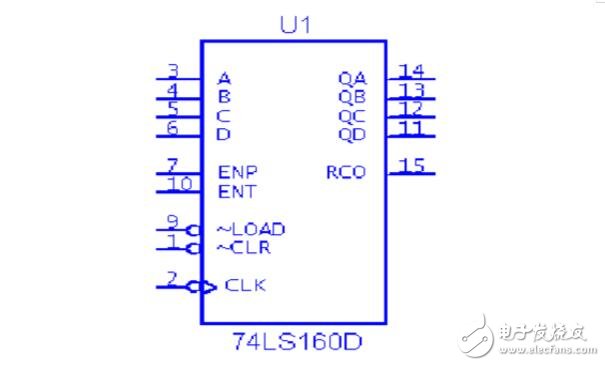

74ls160d引脚图及功能

|

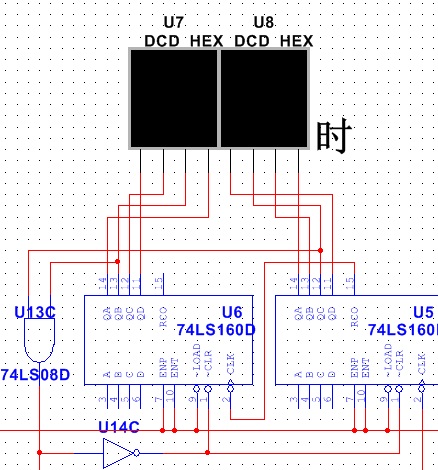

计数译码显示电路实验

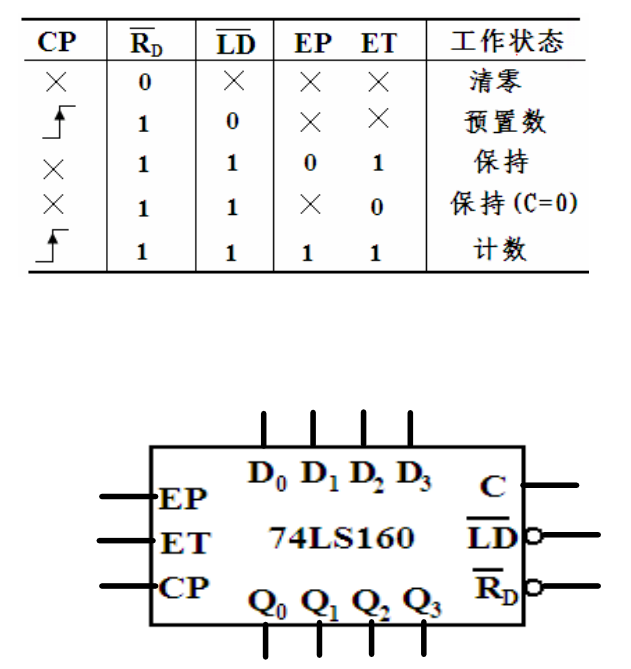

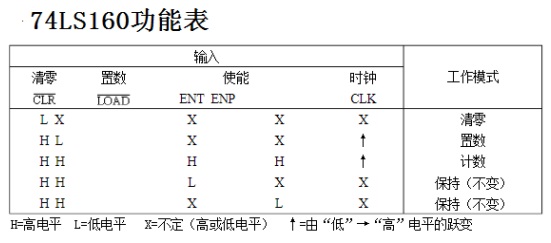

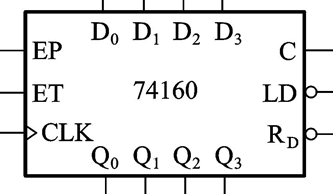

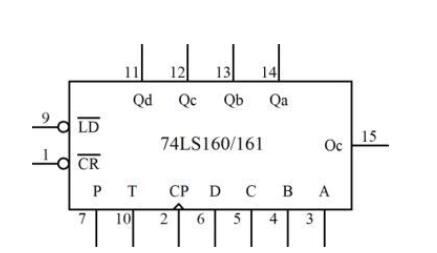

74ls160 集成计数器

74ls160引脚图与真值表

利用置数法把同步十进制计数器74ls160设计一个同步八进制计数器直接

74ls160 逻辑功能见表2

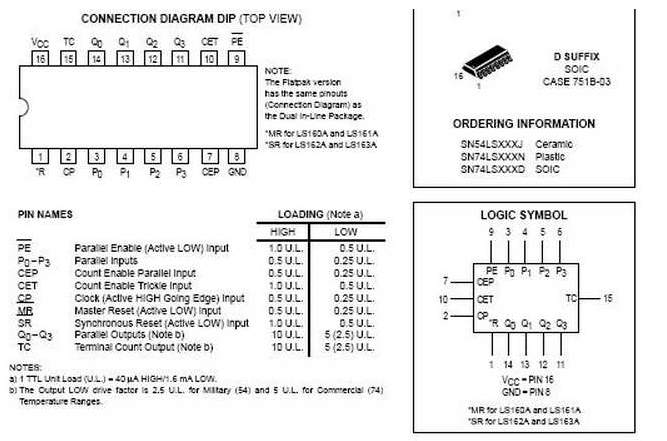

74161引脚功能表

74ls161的管脚排列 的管脚排列

两片74ls160与一片74ls20构成的29进制计数器

74ls160芯片同步十进制计数器直接清零

计算机组成原理 实验

芯片74ls160十进制计数器引脚图及功能

74ls164引脚图及简介(中英文pdf)

74ls161是4位二进制同步加法计数器,除了有二进制加法计数

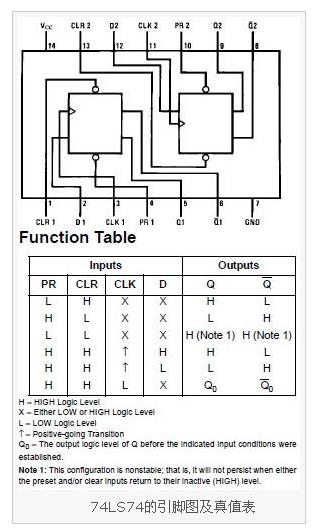

双d触发器74ls74

(2)74ls74引脚图

同步十进制计数器74ls160

74ls160引脚图与真值表

74ls161是4位二进制同步加法计数器,除了有二进制加法计数

74ls160数字电路数字电子钟电路设计

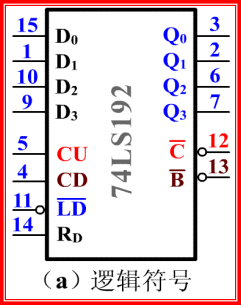

逻辑符号▲ 74ls192功能表各引脚功能符号的意义:d0~d3:并行数据输入

74ls74引脚图及真值表

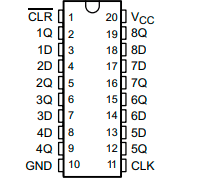

sn74ahc273nsr八路d类触发器芯片中文资料pdf数据手册引脚图产品手册

扩展时所用芯片2 373引脚功能 373引脚功能 d0~d6 d0 d6 e g q0~q7 q0

同步计数74ls160引脚图与功能说明rco 进位输出端enp 计数控制端qa

电子教案《数字电子技术》(雷建龙)教学课教学课件3

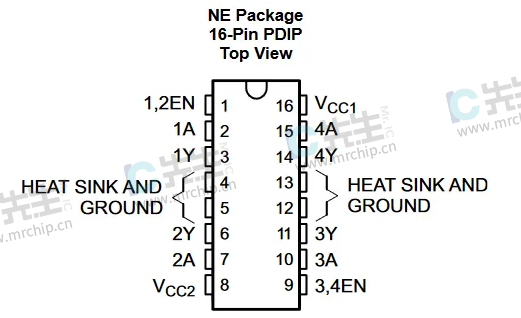

l293d电机驱动器引脚配置

74ls160数字逻辑芯片的工作原理

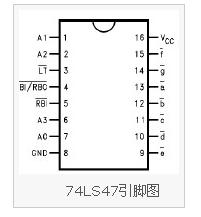

74ls47引脚图

74系列数字电路7417574ls175四d型触发器带清除端

由同步十进制加法计数器74ls160构成一数字系统如图所 |

-

请勿采集本站,如有疑问请联系管理员!