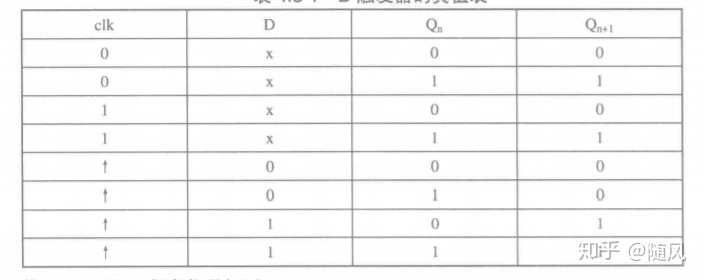

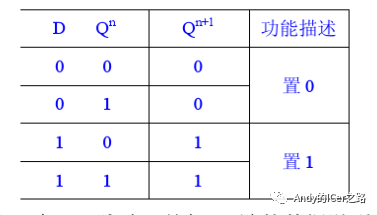

多个d触发器状态转换真值表

|

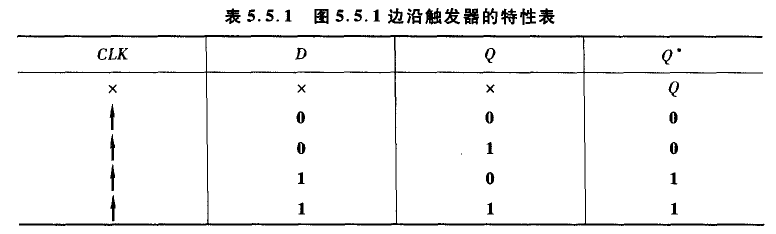

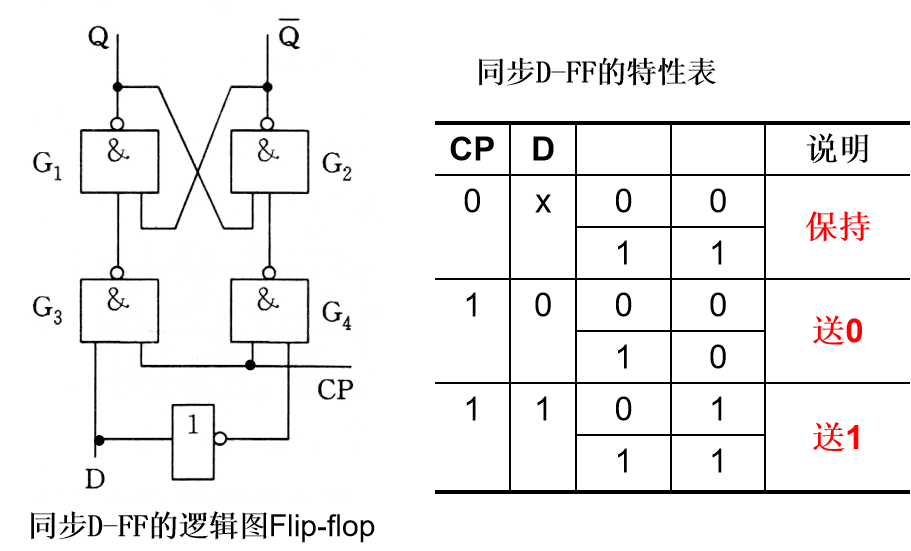

这种触发器的逻辑功能是:不论触发器原来的状态如何,输入端的数据d(无

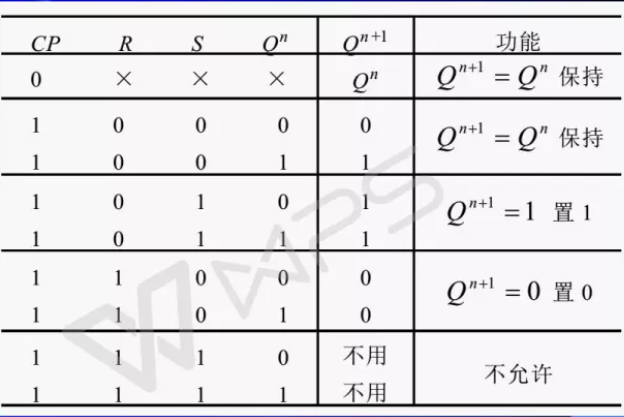

2,特性表1,同步rs触发器

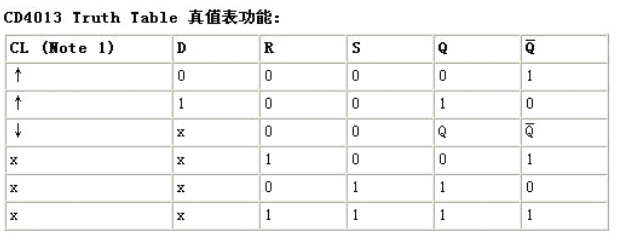

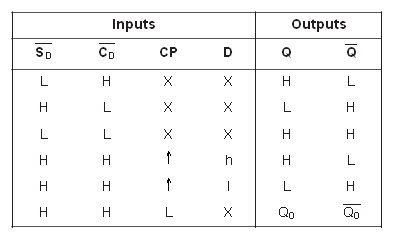

其功能表见表4,由表可知,当rd= 0时,不论cp,d如何变化,触发器可实现

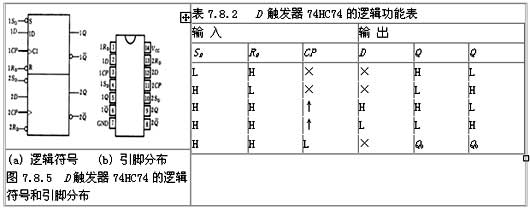

关于双d触发器,74hc74d

这是d触发器的真值表,我想问一下,假如说在时钟的上升沿触发,其输出为

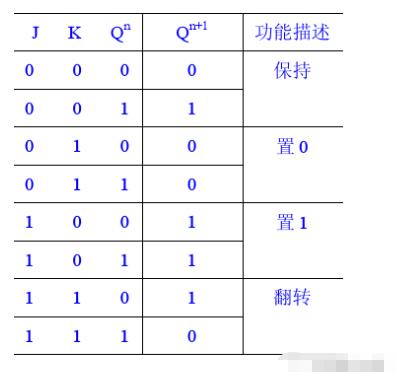

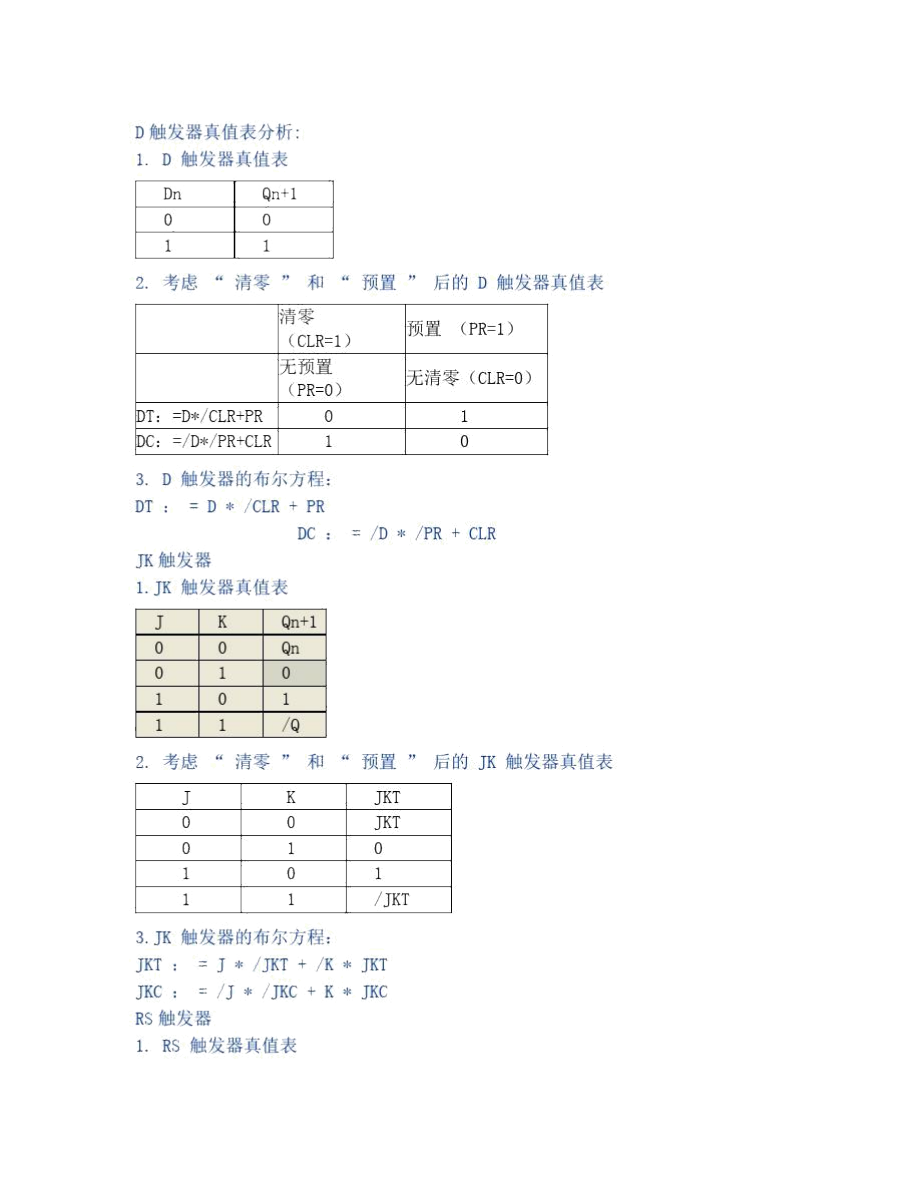

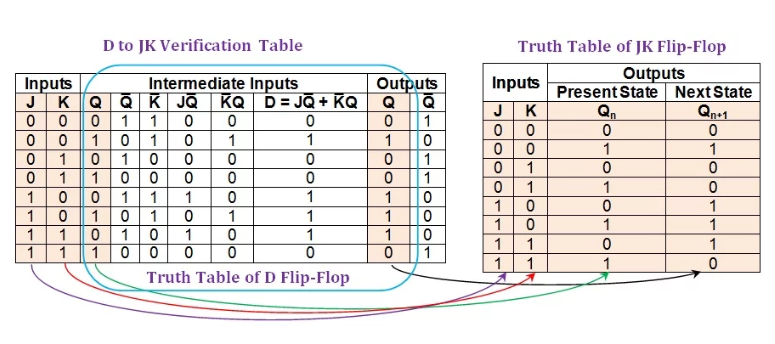

jk触发器d触发器rs触发器t触发器真值表

单元电路设计 1)信号锁存 信号锁存用74ls74正边双d触发器

5,d触发器jk触发器可以很方便地构成d触发器,电路图和真值表如下所示

实验三,基本门电路及触发器电子版实验报告ppt

d触发器功能真值表

k连起来,作为一个输入端t,就构成t触发器了,电路图和真值表如下所示

jk触发器d触发器rs触发器t触发器真值表

5中的逻辑符号和d触发器74hc74的逻辑功能表我们可以看出,hc74是带有

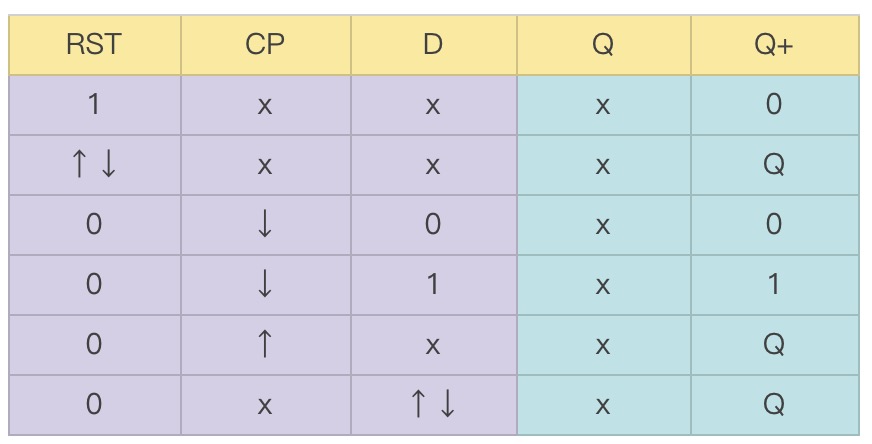

d 触发器的真值表:可见此真值表中还加入了上下沿的概念,是为了

jk触发器d触发器rs触发器t触发器真值表doc2页

jk触发器d触发器rs触发器t触发器真值表

jk触发器d触发器rs触发器t触发器真值表精编版

jk触发器d触发器rs触发器t触发器真值表doc2页

二,边沿触发的触发器(常叫触发器)

相互独立的数据型触发器构成

工学 基于d触发器的异步八进制加法计数器的设计 用simulink仿真 化

能够存储1位二值信号的基本单元电路统称为触发器(filp

jk触发器真值表:可见,当j=k=1时,每次cp由0转为1后触发器状态翻转,也

数电day05 触发器(基本rs触发器,钟控rs触发器,钟控d触发器,钟控jk

表526 d触发器74hc74功能表

每个触发器有独立的数据,置位,复位,时钟输入和q及q输出,此器件可用作

是这些触发器只有在同步信号到达时才按输入信号改变状态

例如将j

22 同步rs触发器的特性表回忆:同步rs触发器的逻辑功能?2

(ω)我系真值表菌 |