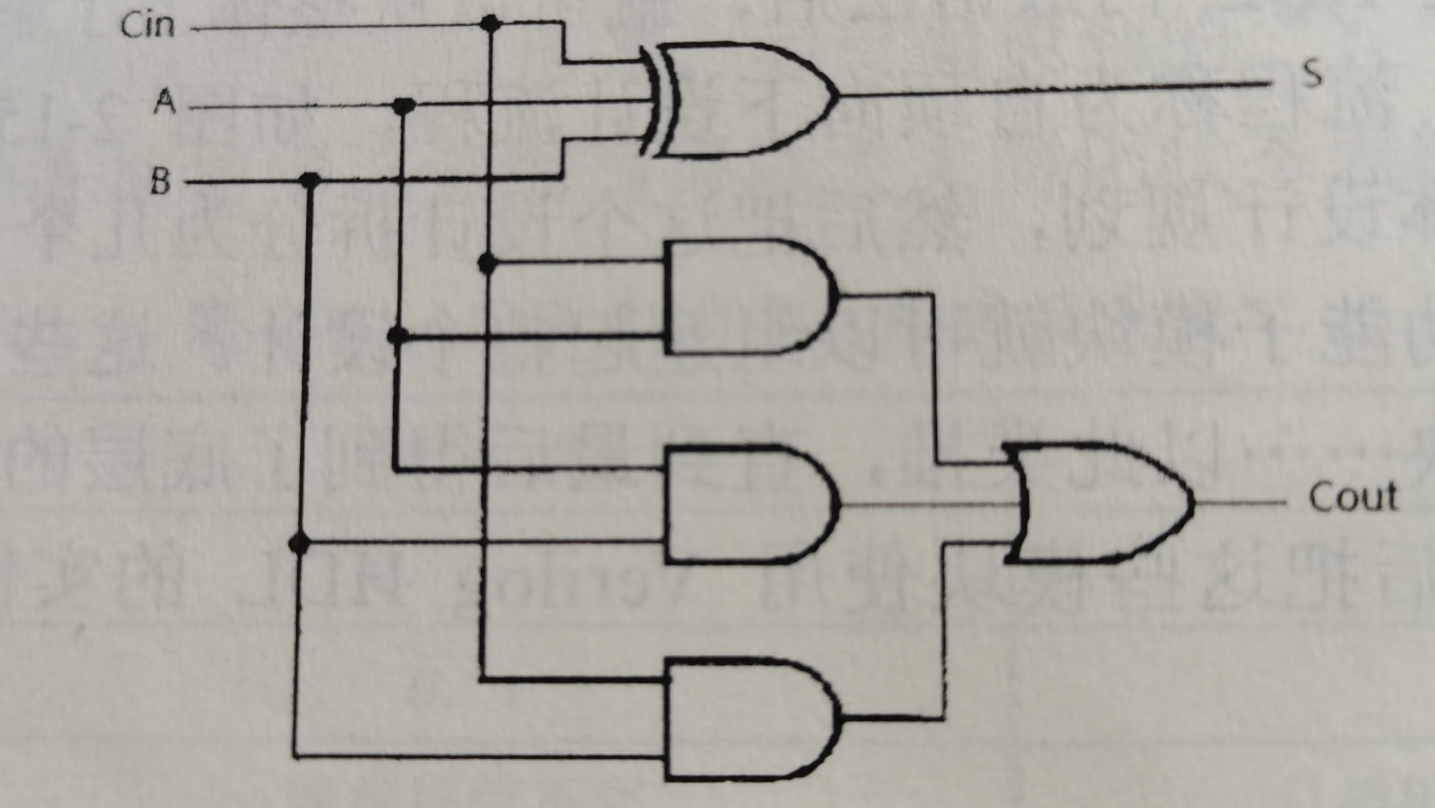

全加器组合电路的逻辑功能测试引脚图

|

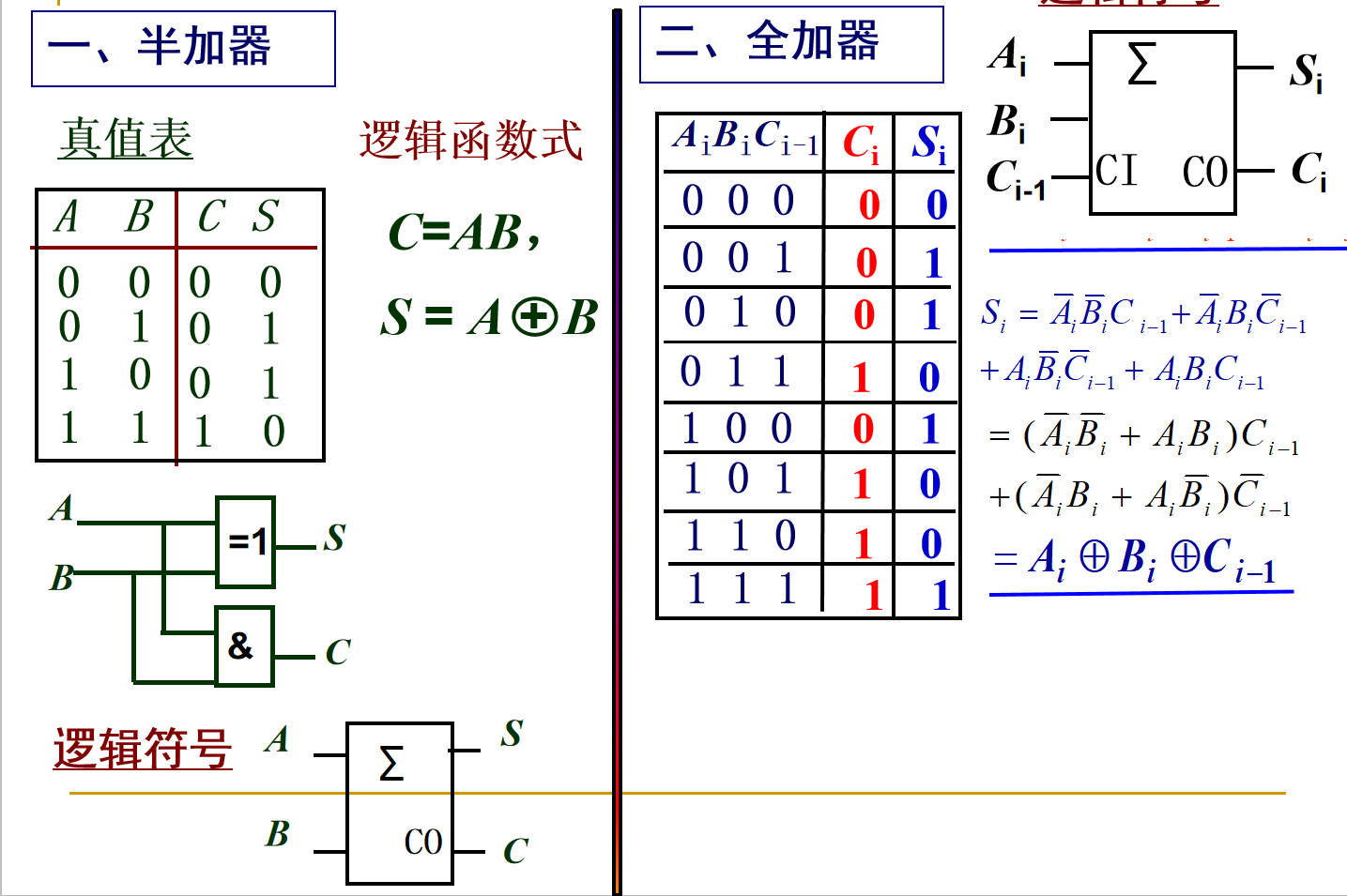

数字逻辑实验 中规模集成组合逻辑电路的应用 求逻辑电路图及逻辑

电子/电路 一位全加器实验电路方法的研究 4 种门电路来实现,逻辑电路

一位全加器电路图

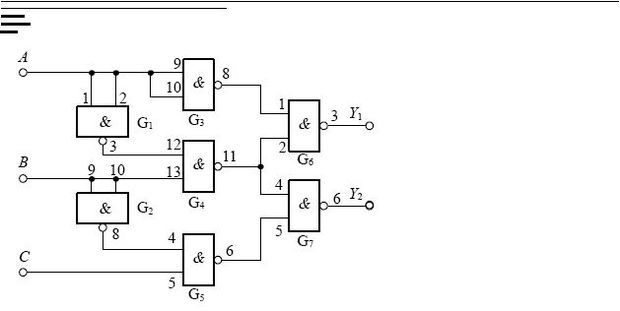

求用两片74ls138设计一个全加器的电路图?

全加器电路

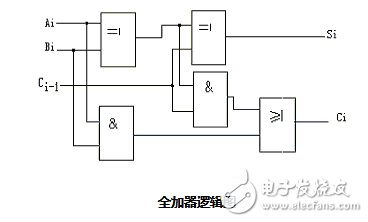

全加器逻辑电路图

全加器,要求有实验原理,函数表达式,卡诺图,逻辑电路图和proteus模拟

数字电路与逻辑设计:用74138实现一位全加器!

9,连接电路,测试逻辑电路输出数据,并记录结果;a ibc i

74ls0074ls0874ls32全加器的ad原理图和pcb源文件

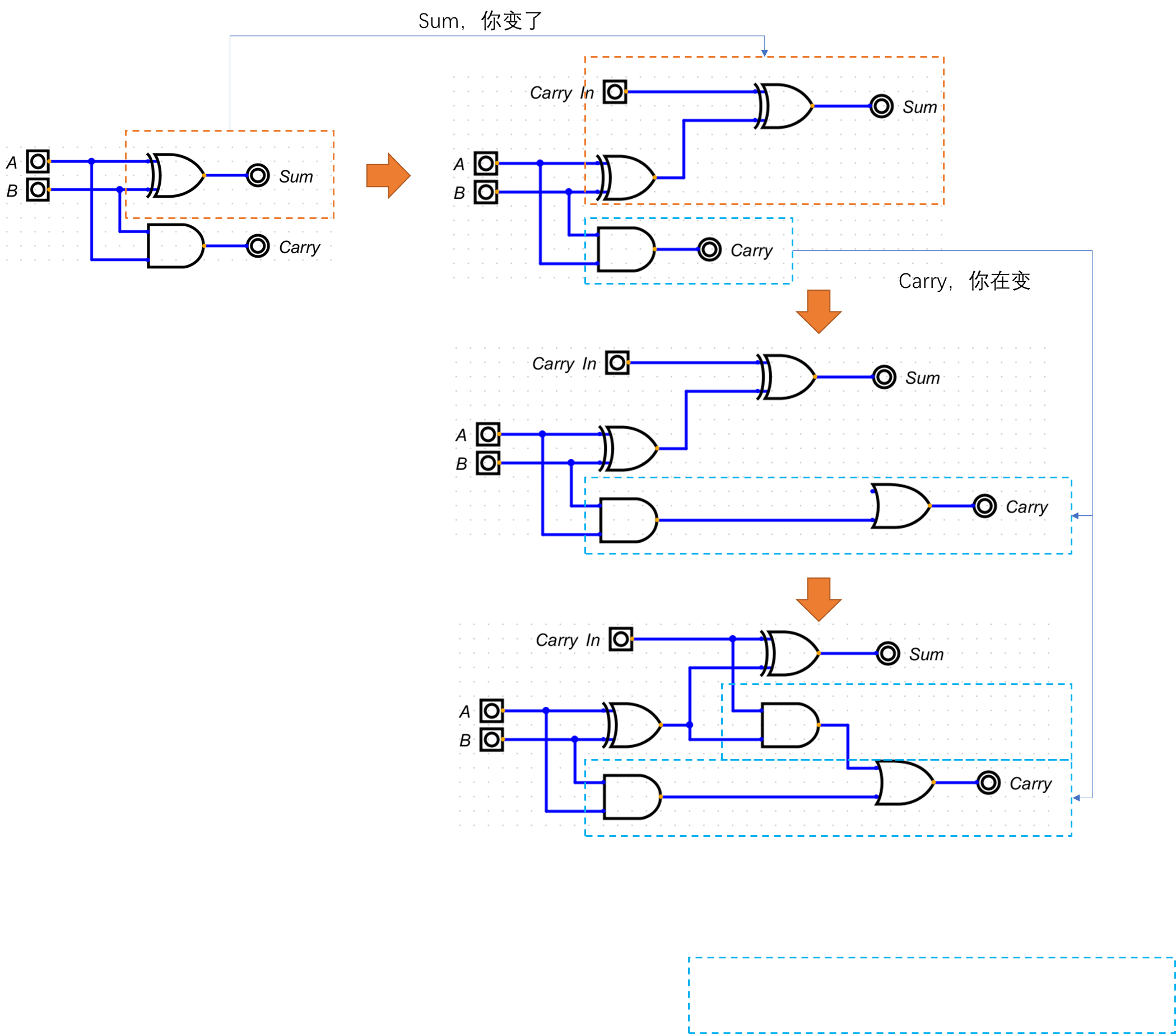

一个bit的加法器(全)

学会组合逻辑电路的功能测试 2 验证一位全加器的逻辑功能 3

5实验数据记录以及实验结果 全加器实验测试结果满足全加器的功能,真

加法电路图如p1所示,根据对应a8

使用全加器的4位加法运算电路图

一位全加器的多种实现方法1ppt

采纳答案 这个逻辑图的功能是两个一位二进制全加器电路

数字逻辑电路——第四章 组合逻辑电路

华理数字逻辑实验二全加器

eda技术讲义 eda技术讲义 全 加 器 被加数,加数以及低位的进位三者

四位二进制全加器74ls283接成正常工作状态, 当a4a3a2a1输入1100,b4b3

逻辑电路图 ③使用全加器元件,设计8位串行进位加法器电路

数字电子技术里四位2进制全加器怎么设计

使用全加器的4位加法运算电路图

全加器电路,包括:数据输入电路模块,数据输入电路模块包括逻辑与门和

74ls138和74ls20设计的三人表决器

的1位全加器构成8位全加器, 并完成编译,综合,适配,仿真和硬件测试

数字电路与逻辑设计:用74138实现一位全加器!

如图所示由集成四位全加器74ls283和或非门构成的电路,已知输入dcba为

如何只用与非门实现全加器,求逻辑图 |

-

请勿采集本站,如有疑问请联系管理员!